SERVICIO AL CLIENTE +593 96 904 5511

Circuito Integrado 74-76

Flip Flop tipo JK.

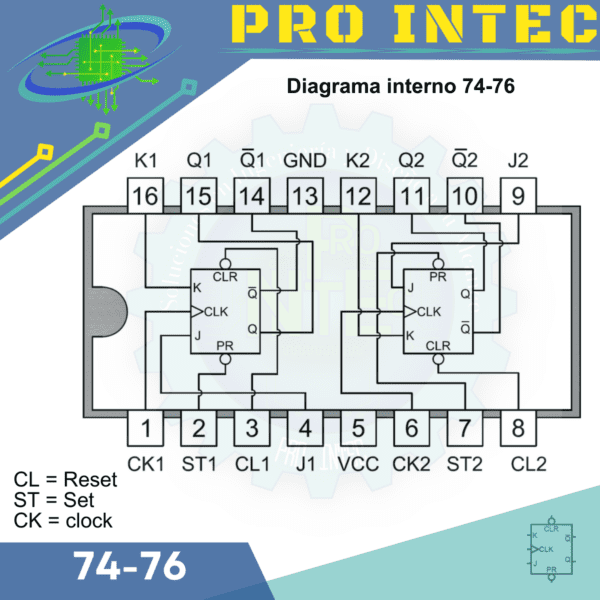

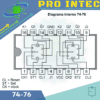

El circuito integrado 74-76. Flip Flop tipo JK. Este dispositivo contiene dos Flip-Flop J-K independientes activados por pulso positivo con salidas complementarias.

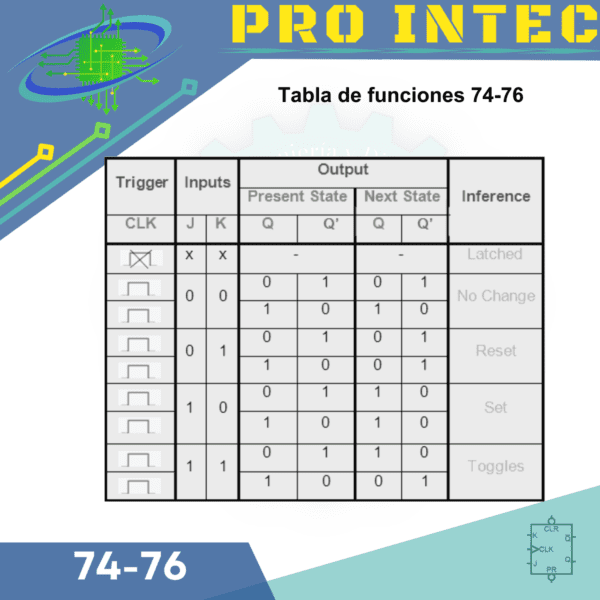

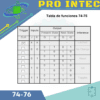

Los datos J y K son procesados por el Flip-Flop después de un pulso de reloj completo. Mientras el reloj está BAJO, el esclavo está aislado del maestro. En la transición positiva del reloj, los datos de las entradas J y K se transfieren al maestro. Mientras el reloj está en ALTO, las entradas J y K están deshabilitadas. En la transición negativa del reloj, los datos del maestro son transferido al esclavo.

No se debe permitir que el estado lógico de las entradas J y K cambie mientras el reloj esté en ALTO. Los datos se transfieren a las salidas en el flanco descendente del pulso de reloj. Un nivel lógico BAJO en las entradas preestablecidas o borradas activará o restablecerá las salidas independientemente de la lógica.

Información Adicional

Función Lógica: Flip Flop tipo JK

Tipo de Montaje: Montaje en orificio pasante

Tipo de salida: normal e inversa (Q y Q’)

Número de entradas: 4 (2 de cada Flip Flop)

Número de salida: 4 (2 de cada Flip Flop)

Pines: CLK, set, reset (para cada Flip Flop)

Tipo de Encapsulado: DIP

Conteo de Pines: 16

Familia Lógica: LS

Tensión de Alimentación: 5,25 V

Corriente de consumo: 15 mA

Temperatura Máxima de Funcionamiento: +70 °C

Temperatura de Funcionamiento Mínima: 0 °C

Descargable

para mayor información puedes descargar la hoja de datos.Datasheet